Can you see how this might work as a piece of memory? Imagine a single bit of data being stored in the Q output!.There shouldn't be any effect on Q or its complement. Now Q should 'set' and go high, while Q goes low. Q should "reset", if it wasn't already 0, it will become 0.

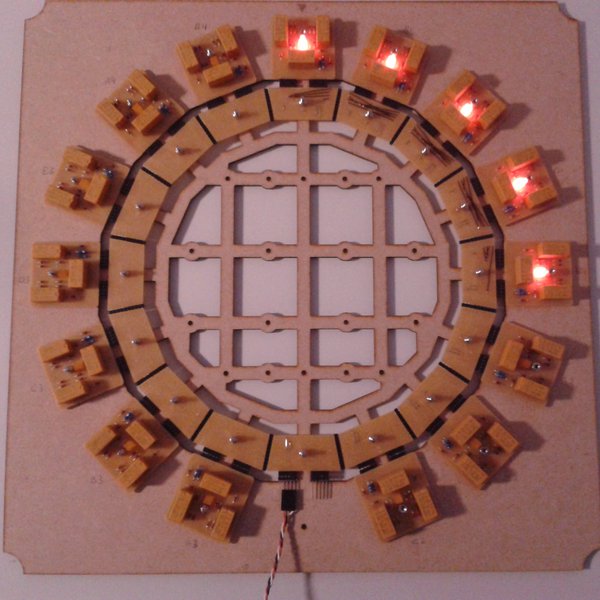

We need an initial state to start us off.Give this series of steps a try, and observe both Q and Q outputs. Our Q output is indicated by the red LED on the NOT gate fed by the OR gate with R as its input. The NOT gate coming out of the OR gate with S as its direct input indicates the Q output. There are two outputs to keep an eye on in this circuit both are indicated by the red LEDs on the NOT gates. Because the circuit is symmetric, it doesn't matter which input we call which, but the name of the input will affect which output is which. One should be R (reset) the other should be S (set). In our mind, we need to assign names to both inputs. We can also use a state diagram to document the possible states of Q: Our LogicBlock circuit isn't quite that smart, so you'll need to take the "circuit safety" precautions into your own hands to make sure they're never both 1 (don't worry, the universe should survive the contradiction if you set both inputs high). In most latch circuits precautions are taken to keep those inputs from both being 1. So we call S=1/R=1 a restricted combination. Restricted: When both S and R are 1, we enter restricted territory: our rule that Q and Q must be complements is broken, as they both go to 0.If Q was already 0, though, R won't have any effect on it. As long as Q was 1, setting R to 1 will change Q to 0. Reset: Moving the R input from 0 to 1 can "reset" Q.If Q was already 1, making S=1 will have no effect. If Q was 0, changing S to 1 will change Q to 1 as well. Set: Changing S to 1 has the potential to "set" the output of Q.If it was 0 it'll remain 0, if it was 1 it will still be 1. Steady: When S and R are both 0, then Q remains steady.Put into words, the output, Q, can be in any of the following states: Because the circuit is sequential, the current value of Q depends on its previous state: SĠ (Restricted, Q and Q would not be complements) Here is the state table, which is a bit wonky. We can add an enable input to the ring oscillator by introducing an AND gate. When the enable input is set to 1, the circuit operates as normal, but when its set to 0 the circuit's operation is halted. Enable inputs - commonly found in many digital logic circuits - control the overall operation of the circuit. In some cases it may be handy to have an enable input on your oscillator. What effect would increasing the number of inverters to 5 have on the blinking rate of the output? Can you calculate how fast the LED on the final NOT Block is blinking? Each block has a delay of about 1 second.Does the number of inverters have to be odd? What happens if there are an even number of inverters? Try removing one of them.Does it even have a truth table? There aren't any inputs! Instead of a standard truth table, we can create a state table that defines the value of the current output as dependent on the previous output: Previous Output What does the truth table look like for this circuit? Wait. The output of this circuit is represented by the red LED on the third and final NOT block.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed